英特尔的全新网格架构:数据中心的“超级高速公路”

时间:2017-06-16 来源:互联网 浏览量:

数据中心架构的一个重点就是提高效率,以便获得最佳资本回报并在有限的空间和电力下最大程度提高数据中心的输出。处理器在数据中心优化中起着根本性作用,处理器架构的选择对可扩展性和效率有着巨大的影响。要想在这些因素之间达到理想的平衡,就需要远见、创造性和创新,而这些并不能一蹴而就。

英特尔广泛的产品组合中体现了其数十年设计专用数据中心CPU和平台的丰富经验。一代又一代,英特尔不断创新核心计算功能,以期提高处理器性能。但是我们的工作并未止步于此。所有内核的连接和可扩展性的改进、对内存层次结构进行微调、增强I/O也同样重要,这些因素将确保组成数据中心主要构建模块的计算、网络和存储系统的可扩展性和效率。

成长的烦恼:规模所带来的挑战添加更多内核并将其连接,以便创建一个多核数据中心处理器,这个任务听上去可能很简单,但是CPU内核、内存层次结构和I/O子系统在这些需要周密架构子系统的连接提供了关键路径。这些互联就像一个精心设计的高速公路一样,在关键位置设有合适数量的车道和坡道,以便让交通一路畅通,而不是让人们和货物闲坐在路上浪费时间。

增加处理器内核的数量并提高内存和每个处理器的I/O带宽,以满足大量数据中心负载的需求——这构成了一些必须通过创造性架构技术才能解决的挑战。这些挑战包括:·提高内存、片上缓存层级架构、内存控制器和I/O控制器之间的带宽。如果可用互联带宽并不能随处理器上的其它资源适当扩展,那么互联就会像令人沮丧的高峰期交通拥堵一样,成为限制系统效率的瓶颈。

·降低访问来自芯片缓存、主内存或其它内核数据时的延迟。访问延迟取决于芯片实体之间的距离、发送请求和响应的路径,以及互联操作的速度。这相当于在扩张型城市vs紧凑型城市的通勤时间、可用路径的数量,以及高速公路上的限速。·创造高能效的方式,把数据从芯片缓存和内存提供到内核和I/O。由于每个组件之间更远的距离和更高的带宽,当添加更多内核时,完成相同任务的数据迁移所需的能量就会相应地增加。以交通为例,随着城市成长和通勤距离的增加,通勤期间所浪费的时间和能量会让用于生产工作的可用资源变得更少。

英特尔致力于创新架构解决方案,以便在创建更强大、高效的处理器时走在挑战的前面,从而满足现有和新兴工作负载——例如人工智能和深度学习的需求。

英特尔运用其经验和创新技术,为即将推出的英特尔? 至强?可扩展处理器开发了新架构,以便为现代数据中心奠定可扩展的基础。这些新架构提供一种新的方式来互联片上组件,以便提高多核处理器的效率和扩展性。

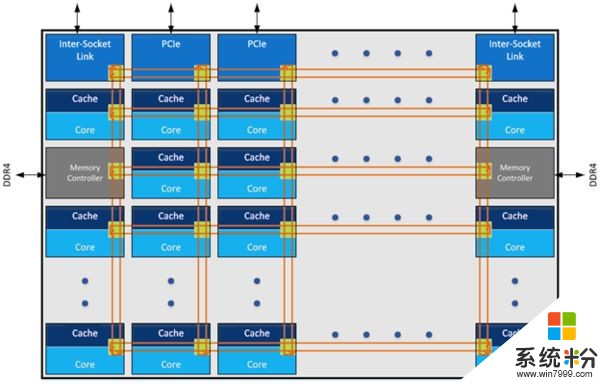

Figure 1: Mesh architecture conceptual representation

图1:网格结构概念示意图

英特尔 至强 可扩展处理器采用一个创新的“网格”片上互联拓扑结构 (Mesh),可在内核、内存和I/O控制器之间提供低延迟和高带宽。图1显示了该网格架构的示意图,内核、芯片缓存库、内存控制器和I/O控制器是按照行和列而组织的,在每个交叉口通过线和 交换机 而把它们连接在一起,以便允许转弯。通过提供一个比之前环形架构更加直接的路径,以及更多通道来尽量减少瓶颈,网格可在更低的频率和电压下工作,并仍能实现非常高的带宽和低延迟。这使性能得以提高、能效得以增强,就像一个精心设计的高速公路系统,让交通能够在不拥堵的前提下以最佳速度流通。

除了改进片上互联的连接和拓扑,英特尔至强可扩展处理器还采用一个带有可扩展资源的模块化架构,以便访问片上缓存、内存、IO和远程CPU。这些资源分布在整个芯片上,这样就能最大程度减少“热点”或其它子系统的资源限制。该架构的模块化和分布式特性让可用资源能够随处理器内核数量的增加而扩展。

这些可扩展和低延迟的片上互联框架也对共享的最后一级缓存架构非常重要。这些大型共享缓存对于复杂的多线程服务器应用——例如数据库、复杂的物理模拟、高吞吐量网络应用,以及托管多个虚拟机——非常宝贵。访问不同缓存库时可忽略的延迟差异让软件能够把分布式缓存库当作一个大型、统一的最后一级缓存。因此,应用开发者不必担心访问不同缓存库时不同的延迟,他们也不需要优化或重新编译代码即可使其应用的性能得到大幅提升。统一低延迟访问的好处也能惠及内存和IO访问,多线程或分布式应用(涉及不同内核上的执行之间的互动,以及来自IO设备的数据)不需要仔细映射一个插槽内的内核上的协作线程即可获得最佳性能。因此,这种应用可充分利用大量内核,并且仍能实现良好的可扩展性。

总结

采用Mesh的片上互联的新架构提供非常强大的框架来集成英特尔 至强 可扩展处理器的各种组件——内核、缓存、内存和I/O子系统。这种创新架构能够在最广泛的使用场景中提高性能和效率,并为英特尔及其无与伦比的全球生态系统所带来的持续改进奠定基础,从而交付可提供数据中心客户所期待的计算能力和效率的解决方案。

本文来源:C114中国通信网